Kevin Freitas on LinkedIn: FPGA Ethernet project The Xilinx AXI Ethernet Lite MAC supports the Media…

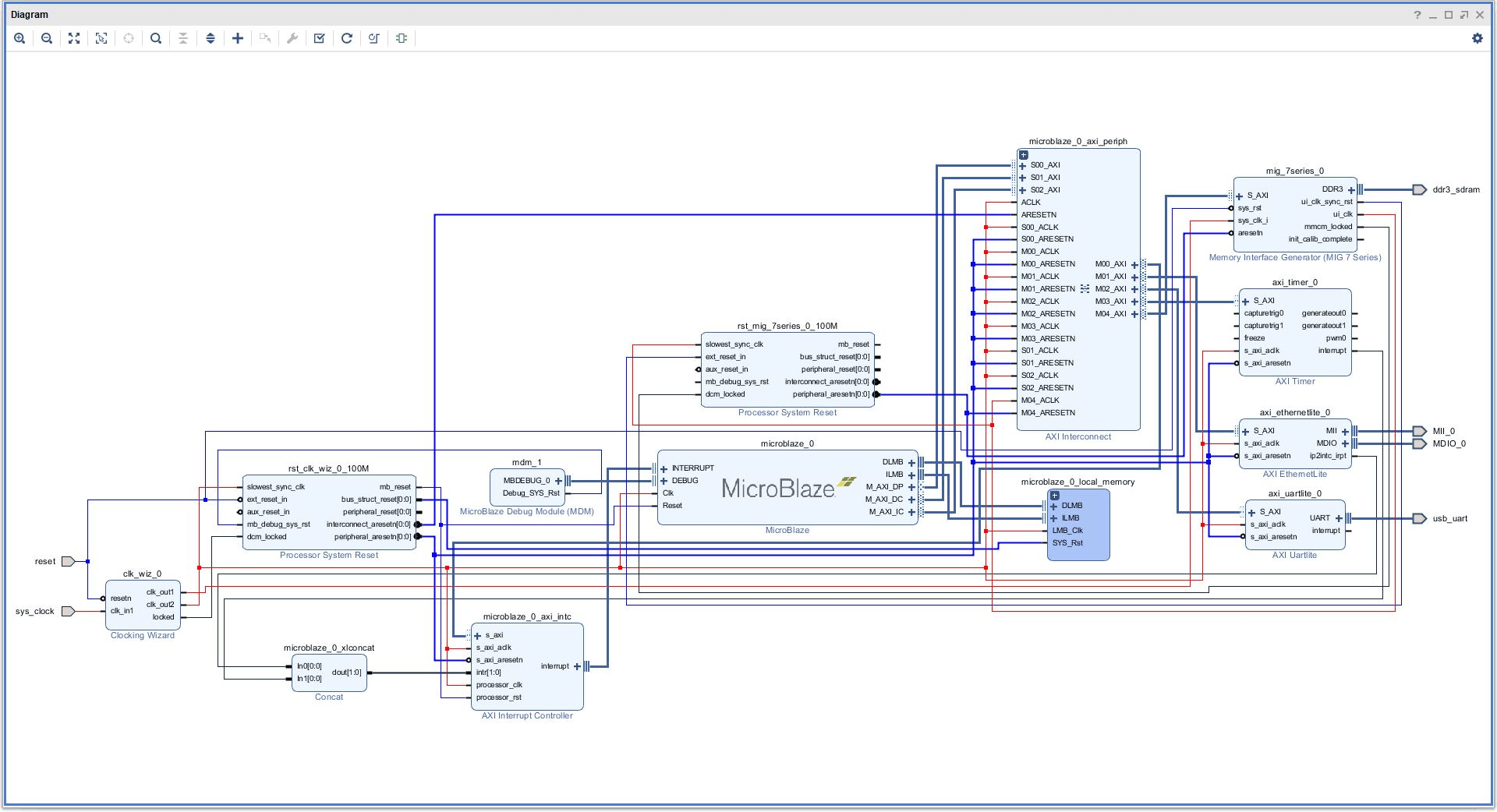

No ping on AXI Ethernet Lite design on KC705 after more AXI peripherals are added to design? : r/FPGA

Implementation of LWIP Echo Server (Axi ETHERNETLITE) without using AXI UARTLITE - FPGA - Digilent Forum